Выдали мне тут троли на одном говнофоруме… говорят мол, “Шодан, бабу тебе надо ! Бабу!”. Ну я немного подумал, подумал, и согласился, да! Мне надо бабу!!!! Конкретно сейчас активно присматриваюсь к “Зинке”…

А почему? А потому, что раз уж нырять с головой в FPGA, то как-то не серьезно брать устаревший Xilinx Spartan-3. Как показала практика старенькая среда разработки Xilinx ISE, которая единственная сейчас поддерживает FPGA Spartan-3, чрезвычайно глючна. Это конечно не является веским поводом менять в дизайне кристалл, но точно это повод чтобы задуматься. Ну вот я и задумался… Осмотрев рынок имеющихся решений, были найдены более-менее свежие FPGA-шки Xilinx Zynq-7000. (Зинки! :-D)

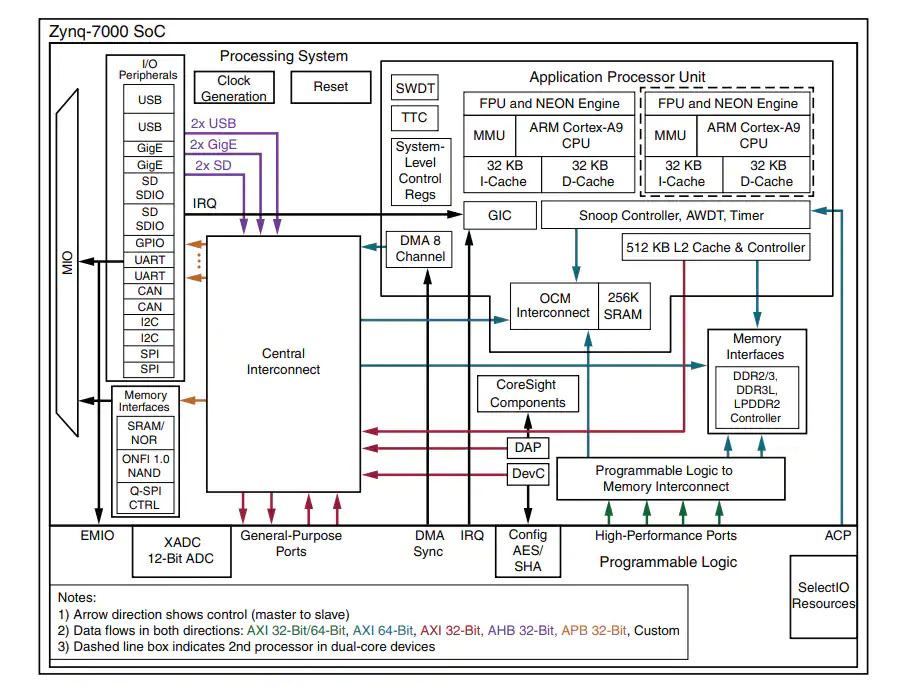

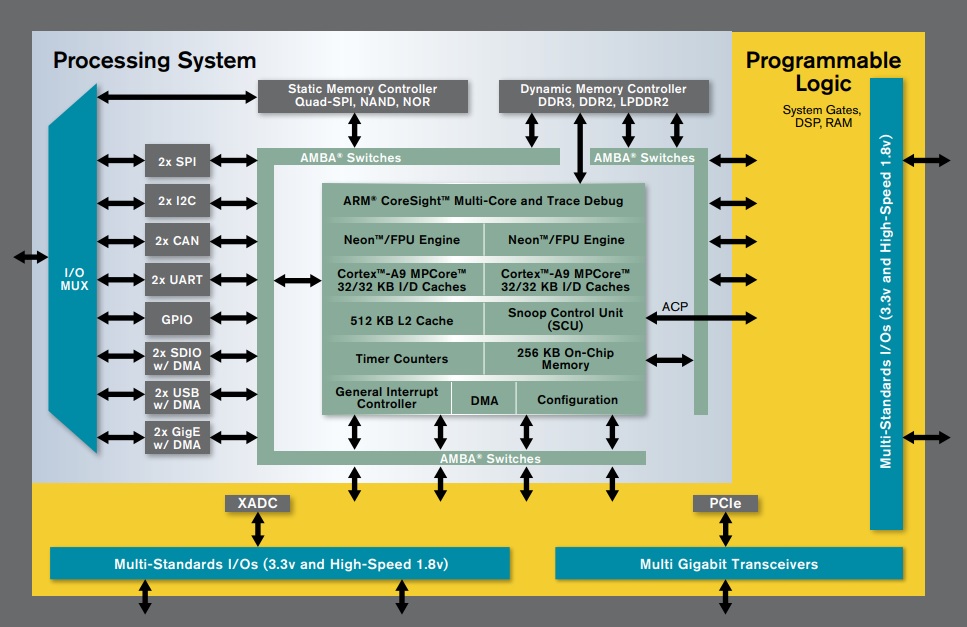

Это в сути своей даже не просто FPGA, а целый систем-он-чип, в котором пол кристалла, это навороченный двухядерный процессор Cortex-A9, с тактовыми частотами под 600 МГц и огромной кучей периферии.

Который позволит полностью отказаться от старенького STM32.

А вторая часть кристалла, это FPGA 7-го поколения Artix-7, в которую влезет любая моя хотелка. И вместе они соединены набором гибко-конфигурируемых шин.

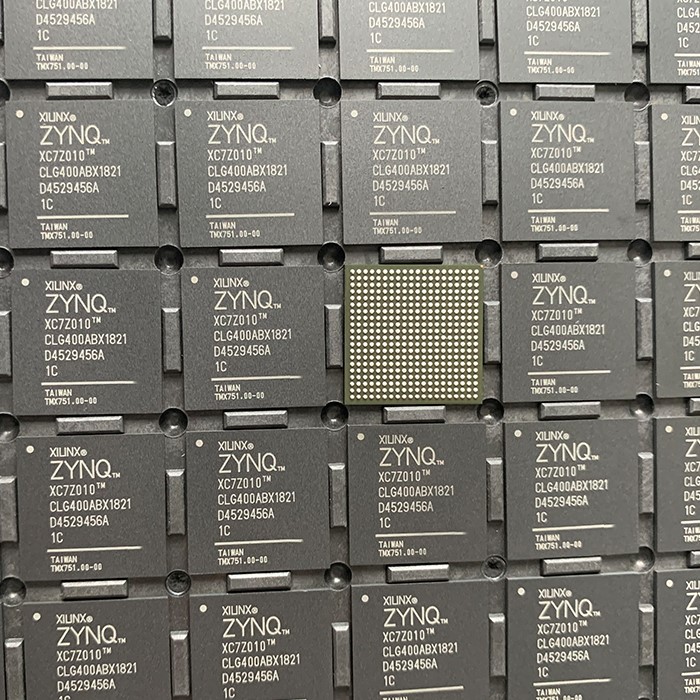

Но собственно почему мой взор пал именно на Zynq-7000, а по тому что младшие чипы этой серии XC7Z010-1CLG400C активно применялись в нескольких видах майнинг-контроллеров. А поскольку пирамида майнинга потихоньку рушится, то огромное количество этих чипов стали не удел.

Их сейчас очень легко купить, в том числе и новые FPGA причем за очень дешево. 200р. за плату донор в неизвестном состоянии, а за 600р. за можно купить напаянный FPGA.

По моим примерным прикидкам, комплект самых-самых базовых деталек для создания на базе этого чипа достаточно гибкого вычислительного модуля должен состоять из:

- FPGA Xilinx XC7Z010-1CLG400C.

- 2xDDR3 SDRAM Micron MT41J64M16JT-125.

- DDR терминатора TPS51206.

- 2xQSPI Flash ISSI IS25LP128.

- USB PHY USB3320.

- PMIC TPS65400.

- И кучки разнообразной рассыпухи.

При этом его стоимость менее 50$ на Алиэкспресс, что вполне допустимо для высокоскоростного комбайна с кучей ОЗУ для хранения логов измерений и огромной матрицы FPGA на 28 тыс. блоков.

А до кучи в новой среде разработки Xilinx Vitis, не только поддерживающие эти чипы, но и даже есть возможность создавать “из коробки” достаточно гибкие DDS с разрядностью слова до 48 бит. Как раз то что нужно!!!

Единственное что реально меня смущает, это BGA корпуса на 4 сотни шаров 0.5мм диаметром, которые я пока не разводил и не паял.

Но я вроде хорошо изучил теорию трассировки высокоскоростных шин и BGA корпусов…. Да и паять их есть чем…. Теперь надо свой скиллс применить на практике!

Короче, если не налажаю с трассировкой платы, то цифровой модуль может получится весьма и весьма гибким. Пока ко мне едет горсть разных чипов, эту часть концепта стоит продумать детальнее.