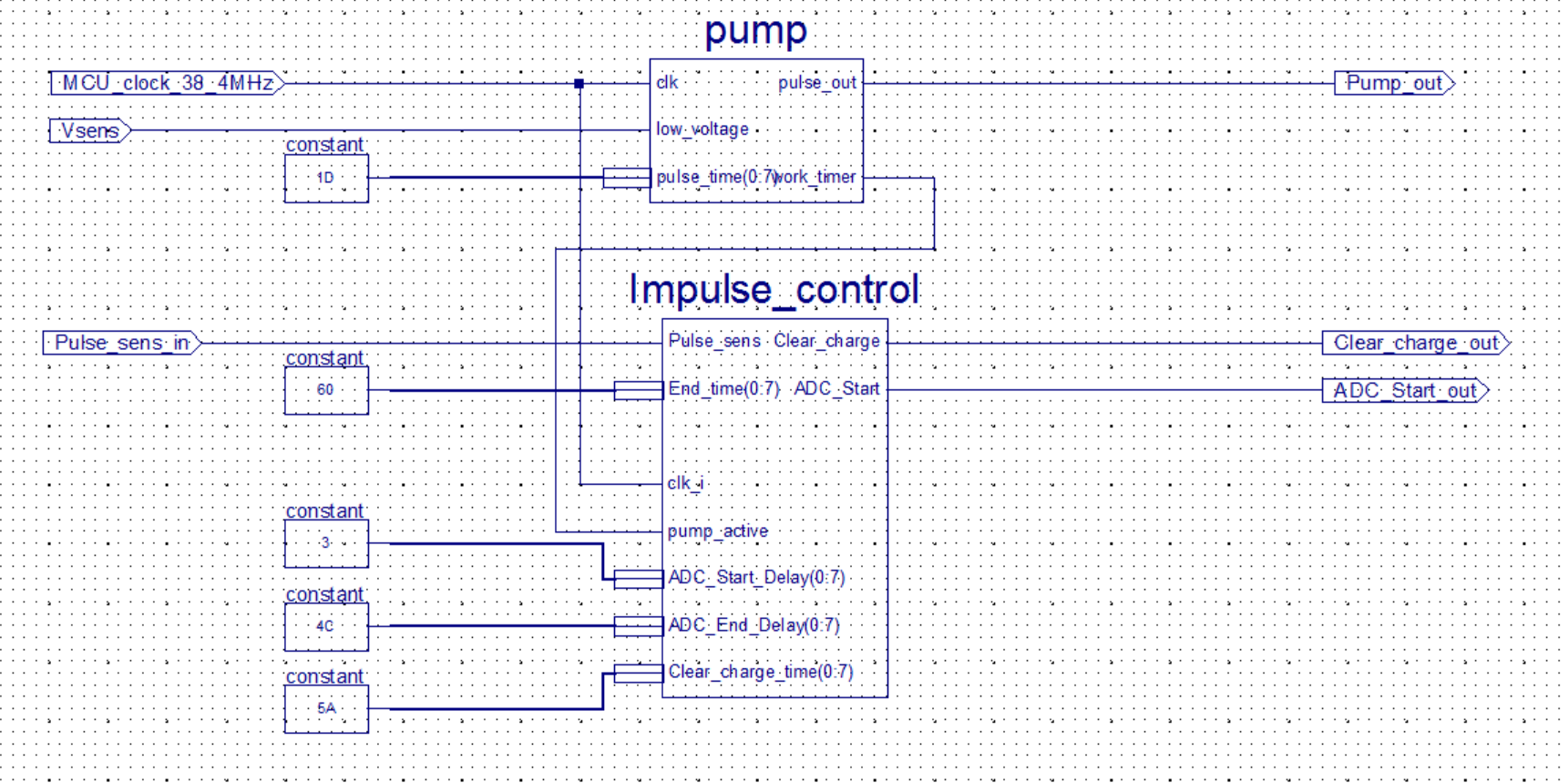

Дорисовал функционал таймеров в ПЛИСине. Решил пока не реализовывать загрузку констант по SPI, в принципе пока для первой редакции их можно прошивать сразу в ПЛИСину на этапе сборки.

Вообщем получилось нечто следующее:

Сигналы:

- Pump_out – накачка на транзистор.

- MCU_clock_38_4mhz – тактовая частота с МК.

- Vsens – уровень с компаратора высокого напряжения.

- Pulse_sens_in – уровень с компаратора анодного импульса.

- Clear_charge_out – управление сбросом заряда в аналоговой цепи.

- Adc_start_out – сигнал для старта АЦП в МК.

VHDL Кодом блока Impulse_control я вас пожалуй утруждать не буду, его всегда можно посмотреть тут. Весь нужный функционал вроде реализовал и занял он около 30% кристалла.

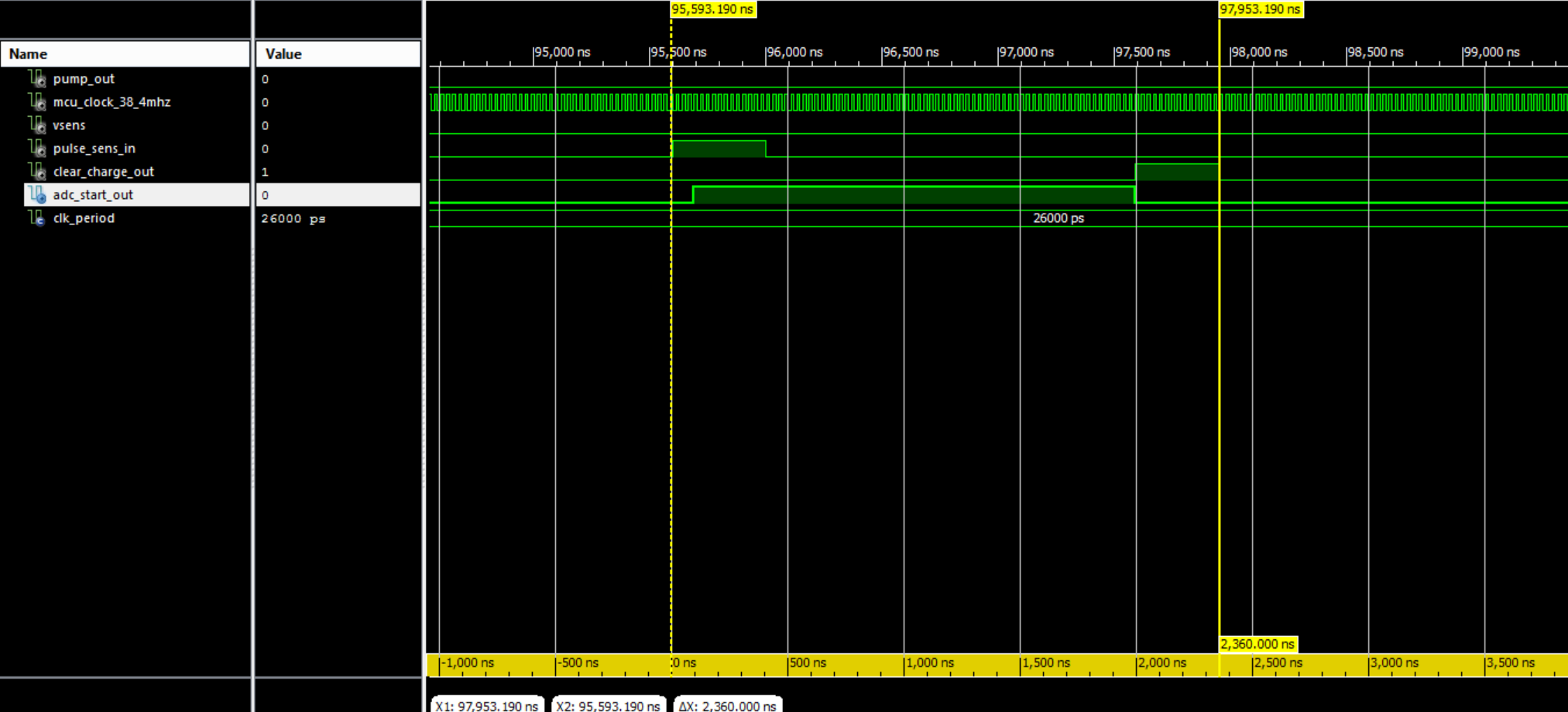

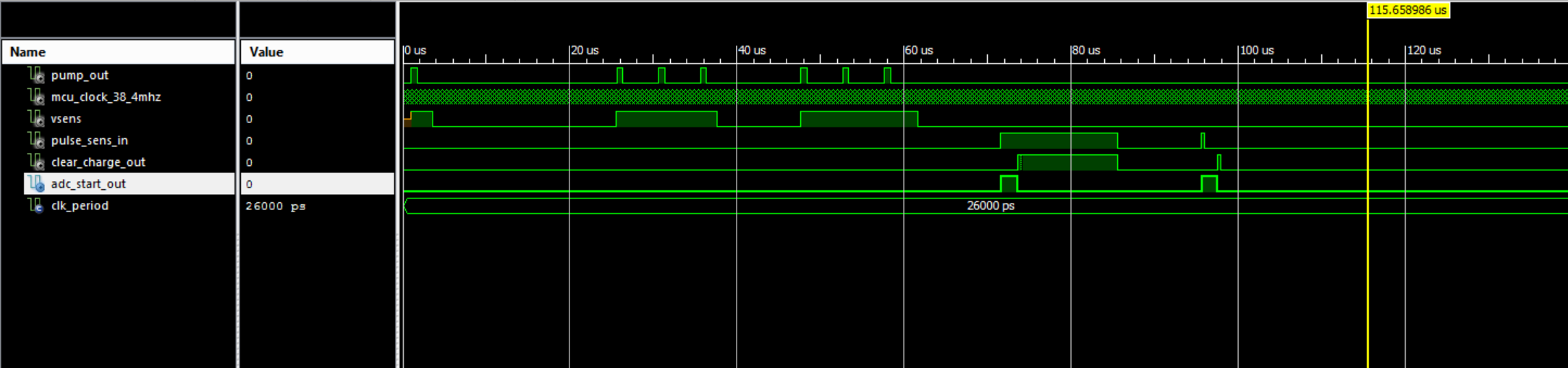

Симуляция работы показывает адекватные результаты:

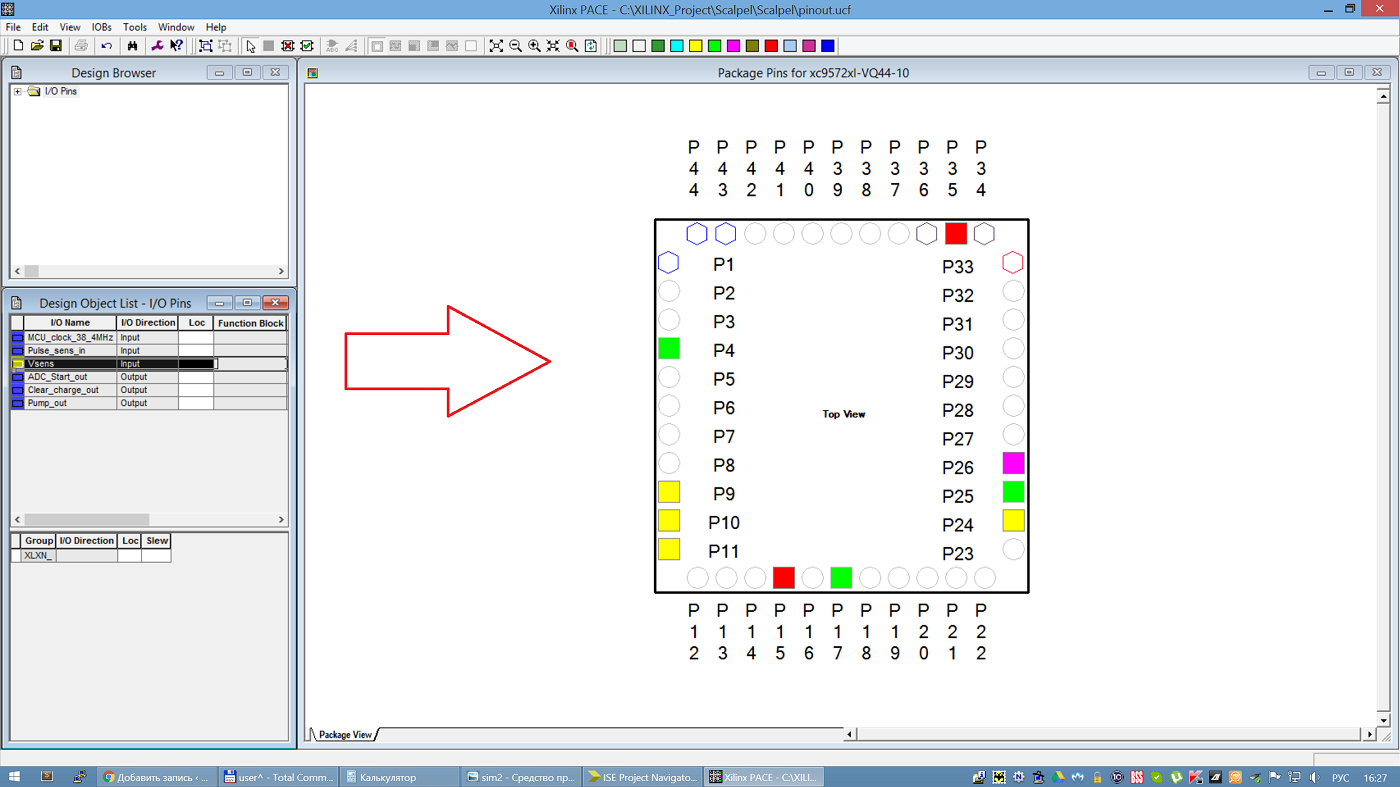

Осталось развести плату. Благо это будет легко. Любой сигнал может быть посажен на любую ножку кроме питания, программирования и основной тактовой частоты.

Вывод: Плисины не так уж и страшны, как кажется на первый взгляд.