Тестирование показывает, что идея деления опорной частоты 10МГц с помощью DDS дает выигрыш, но все эти пляски с бубнами вокруг DDS мне не нравятся концептуально. По этому попробую организовать свое собственное ядро прямого синтеза частоты, минуя стадии генерации аналогово синтеза синусоиды, детекции уровней на триггере Шмитта, и ее дальнейшую дележку т.к. 32-х битного делителя промышленных DDS не достаточно. Заменив все это на истинно цифровой синтез цифрового сигнала LDAC c 64-х битным кодом управления частотой.

По этому после некоторых раздумий, решил таки расчехлить свою “паллету спартанов”, которая лежит на складе в шкафу под названием “до лучших времен”

Простые CPLD тут уже не справятся… Не влезет туда все это разнообразие…

Заодно и VHDL подучу…

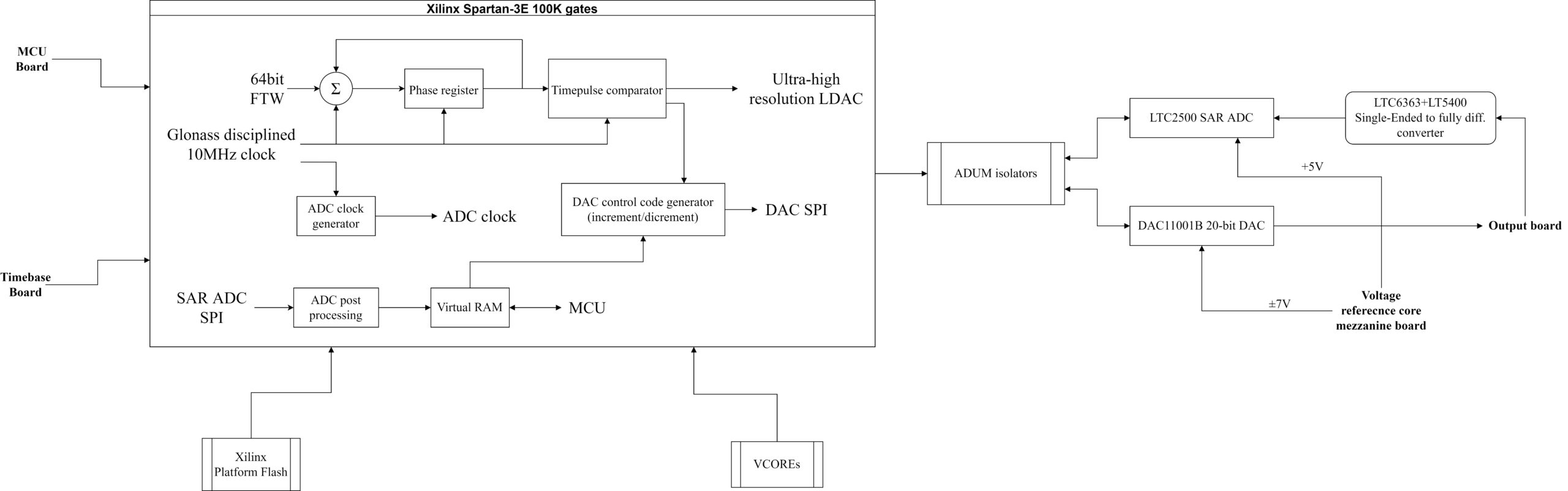

Суть идеи в том, чтобы ликвидировать из концепции Direct Digital Synthesis выходную таблицу синуса с ЦАП, заменив их на прямое сравнение текущего значения фазового сдвига с фиксированным значением. И когда аккумулятор сдвига фазы досчитает до поворота на 360градусов, произойдет событие генерации сигнала LDAC инициирующего смену кода ЦАП. Таким образом концепт сохранит все плюсы концепта Direct Digital Synthesis над простым делением на таймерах, и при этом не будет содержать в своем составе никаких аналоговых цепей. А гарантированный реалтайм обеспечиваемый за счет жесткой логики с контролем таймингов синтезируемой в FPGA, позволит значительно увеличить скорость обновления в ЦАП до полных 75кГц, благодаря чему даже на высоких скоростях ЛИН можно будет сохранить амплитуду шага +-1 LSB (за счет увеличения частоты шагов), что значительно уменьшит выходные шумы ГЛИН. Что не выполнимо, при условии когда ЦАП загружается с помощью МК. Из за чего, при высоких скоростях ЛИН приходилось понижать частоту обновления ЦАП, за счет кратного увеличения шага до +-2LSB…+-3LSB+-4LSB… и т.п. Теперь этот костыль можно будет убрать.

Расчёт показывает, что такой синтез вызовет джиттер до 100нс, связанный с работой аккумулятора фазы, но его и в прошлом варианте не особо удавалось убрать. К тому-же эффект джиттера фронта сигнала LDAC, в значительной степени ослабляется выходным ФНЧ с частотой среза 7Гц, который ослабляет этот эффект в 10 и более раз. А поскольку такой джиттер не будет иметь накопительного эффекта, то он вызовет только переменную составляющую в выходном токе, причем не более 0.1 ppm, что пренебрежимо мало.