Несколько недель я обмозговывал концепт нового детектора, в результате пришел к следующим теоретическим (пока теоретическим, т.к. плата не готова) выкладкам:

Генерация высокого напряжения улучшена по стабилизации:

- Применен монолитный делитель CDHVAF1G00G5000GET с малым ТКС применительно к соотношению плечей ~50 ppm/C.

- Применен новый дизайн детекции напряжения стабилизации, на более чувствительных и быстрых ОУ, при этом плата разведена с уменьшением емкостной связи элементов делителя.

- Опорное напряжение стабилизации генерируется более качественным ЦАП, и вынесено за пределы МК, для улучшения параметров по дрейфам.

- Применен снаббер, для улучшения шумовых характеристик FlyBack преобразователя.

- Шумы пары FlyBack+умножитель дополнительно фильтруются высоковольтной RC группой, для ускорения мертвого времени накачки.

Система снятия импульса:

- ОС выполнена в “беъемкостном” дизайне платы, с минимизацией паразитных емкостей резисторов ОС, с целью максимально возможного ускорения импульса и минимизации экспоненциального емкостного шлейфа.

- ОУ предусилителя заменен на более современный и удовлетворяющий по скоростным характеристикам.

- Добавлена система высокоскоростного счета импульсов для работы с высокими активностями источников.

- Добавлен высокоскоростной управляемый детектор максимума.

- Для управления аналоговой частью с высокой временной точностью и фильтрации шумов накачки была поставлена простая программируемая логика от Xilinx серии XC9500XL.

Питание:

Подсистема питания блока развита до уровня “полный спектрометрический пиздец”, а именно стала содержать следующий минимально необходимый набор питаний:

- Аналоговые +2.5В.

- Аналоговые -2.5В.

- Аналоговые -5В.

- Аналоговые +5В.

- Цифровые +3В.

Общий дизайн

- Все делители и сопротивления заменены на прецизионный металлфилм от Panasonic серии ERA-3AEB с сверх малым ТКС и малыми собственными температурными шумами.

- Плата разделена на блоки, каждый из которых закрыт няшными EMI экранами от давно известного мне Harwin.

- По соображениям импеданса дорожек и экранировки от шумов, плату пришлось делать 4-х слойку, несмотря на общую простоту трассировки.

- Расчетная скорость счета в спектрометрическом режиме, 250 000 имп/c.

PS.На АЦП и полноценную плисину денег уже нехватило….  Поэтому решил выжать предельно возможные скорости из EFR32, передав ему в подчинение свою собственную CPLD-шку, чтобы хоть как-то реализовать нужное управление временными характеристиками на этом говне.

Поэтому решил выжать предельно возможные скорости из EFR32, передав ему в подчинение свою собственную CPLD-шку, чтобы хоть как-то реализовать нужное управление временными характеристиками на этом говне.

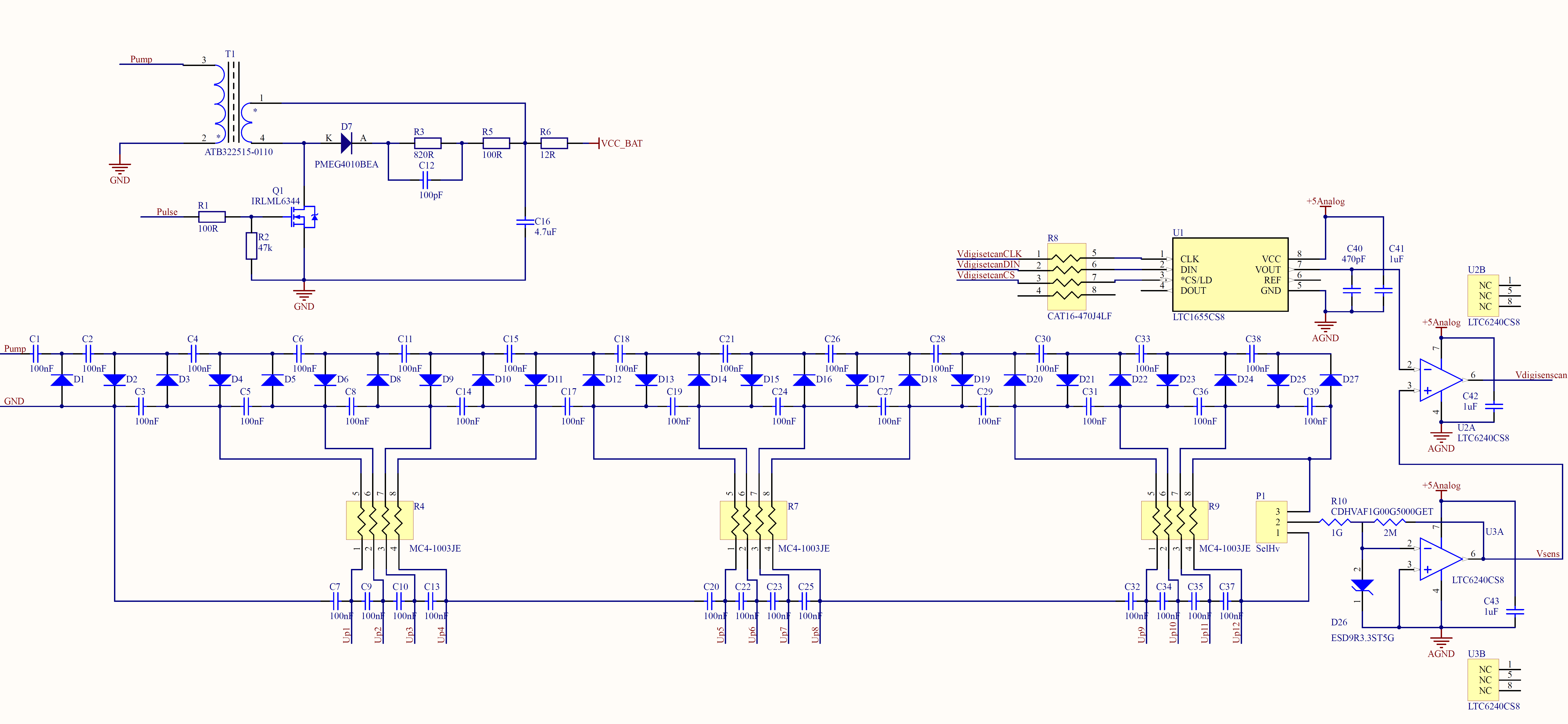

Сразу давать пачкой такие схемы бесполезно, мозг взорвется  Поэтому начну с малого, с питания ФЭУ. Чтоб вы за недельку ее обдумали.

Поэтому начну с малого, с питания ФЭУ. Чтоб вы за недельку ее обдумали.