Что-то я активно занялся тавтологией, и совсем забыл про конкретику.

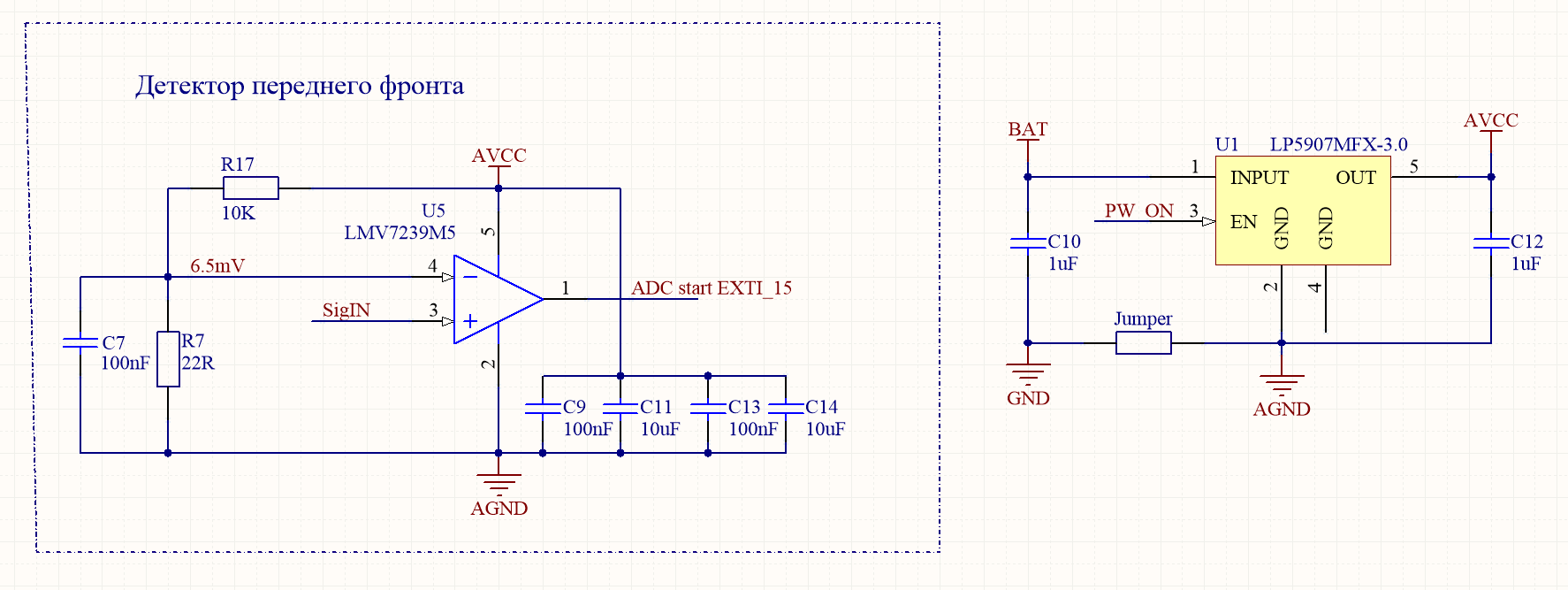

И так, вот проверенный на БДЭГ-е кусочек новой схемы вычислительной платы.

- Заменен аналоговый стабилизатор и его обвязка на более дешевые.

- Детектор фронта был по сути заменен на триггер. Он работает чуть лучше. Начальный канал АЦП не смещается, и нет проблем с резкостью фронта. Но требуется отстройка по шумам, изменением плечей делителя R7-R17.

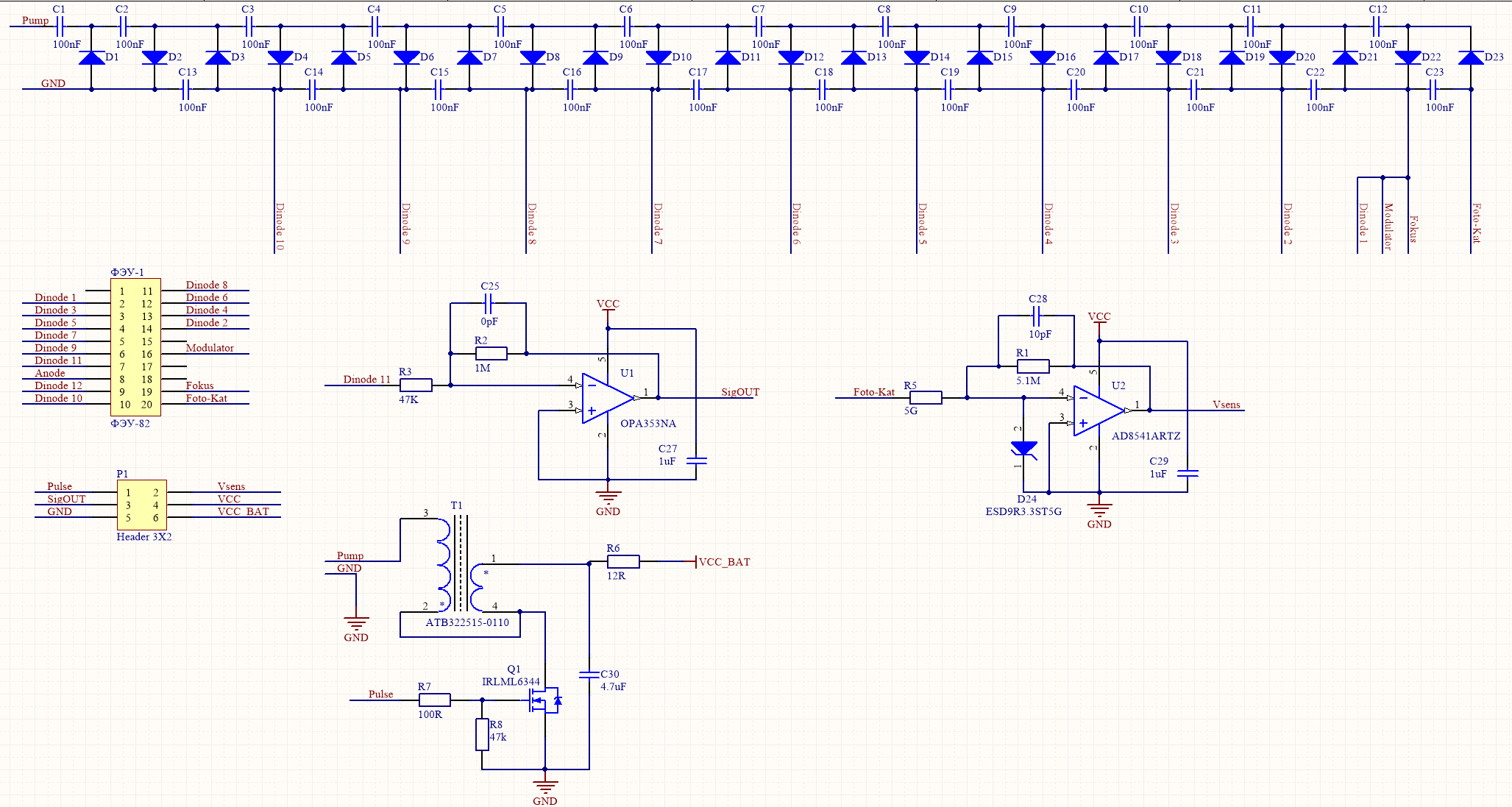

Повышающая плата для БДЭГ2-38, по сути аналог той что была в Модуле-АС.

С тем исключением, что:

- Количество динодов и соответственно длинна умножителя, были увеличены.

- Конденсатор C25 на моих лампах стал ненужен. Но на плате я оставил под него посадочную площадку.

- Номиналы R3 и R2 подбираются в сугубо индивидуальном порядке под каждую конкретную лампочку, основываясь на разрешении.

- Вывод “+” ОУ OPA353NA был жестко посажен на землю.

- Накопительные емкости исключены из схемы в связи с малой их эффиктивностью, при большом усилении ОУ и очень малом анодном токе.

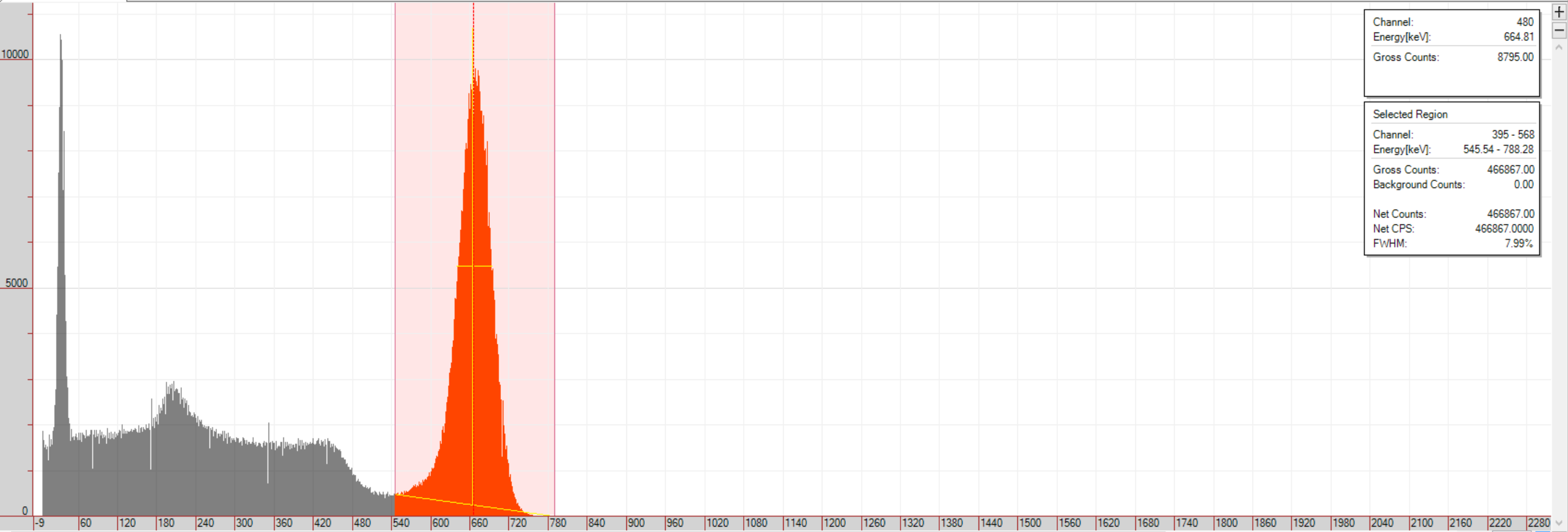

Собственно, на выходе имеем стабильные и не плохие 8.0-8.3%

Да, кончено стоило-бы переделать плату на питание положительным напряжением, но делать этого уже совсем не хочется. Да и платы с отрицательным потенциалом, мало того что спаяны… так они уже в добавок и посажаны на ножки ФЭУ.